$$\begin{array}{l} 1 \\ 1 \\ 1 \\ \end{array} \\ \begin{array}{l} V_{1n} = V_{00} + V_{1p} \\ \hline V_{1n} + \left( V_{p0} + V_{1p} \right) \\ \hline \sqrt{N_p} \frac{W_a}{W_1} \frac{L_1}{L_2} \\ \hline V_{1n} \frac{V_{1p}}{W_1} \frac{W_a}{W_1} \frac{L_1}{L_2} \\ \hline V_{1n} \frac{V_{1p}}{V_1} \frac{V_{20}}{V_1} \frac{V_{20}}{V_1} \frac{V_{20}}{V_2} \frac{V_{1p}}{V_1} \frac{V_{20}}{V_2} \\ \hline V_{1n} \frac{V_{1p}}{V_1} \frac{V_{20}}{V_1} \frac{V_{20}}{V_1} \frac{V_{20}}{V_1} \frac{V_{20}}{V_2} \frac{V_{20}}{V_1} \frac{V_{20}}{V_2} \frac{V_{20}}{V_1} \frac{V_{20}}{V_2} \frac{V_{20}}{V_1} \frac{V_{20}}{V_2} \frac{V_{$$

Hw 14

$$V_{\text{Trip}} = \frac{0.4 + (3.0 - 0.4)}{1 + \sqrt{\frac{250/3}{2.50} \cdot \frac{5}{1}}}$$

$$= 1.64 \text{ V}$$

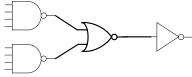

Minimum sized

$$K - input$$

Nor gate

$t_{prop} = \left(\frac{3K+1}{2}\right) t_{ref}$

5)

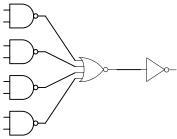

Minimum sized K-input NAND gate  $t_{prop} = \left(\frac{3 + 1}{2}\right) t_{ref}$

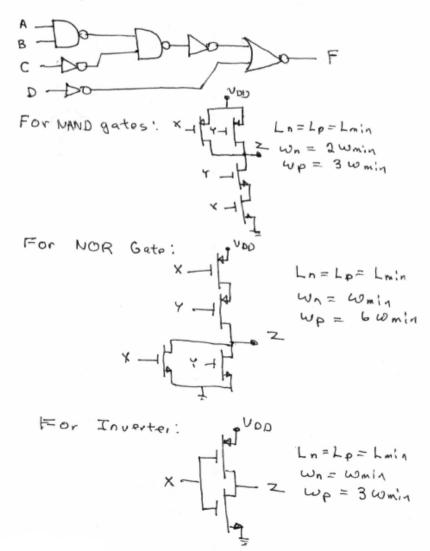

Problem 4 For all inputs, L=Lmin.

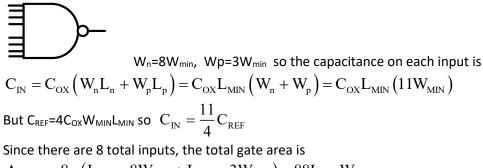

$$A_{GATE} = 8 \bullet \left( L_{MIN} \bullet 8W_{MIN} + L_{MIN} \bullet 3W_{MIN} \right) = 88L_{MIN}W_{MIN}$$

For the inputs on the 4-input NAND gates,  $W_n$ =4 $W_{min}$ , Wp=3 $W_{min}$  so

the capacitance on each input is

$$C_{IN} = C_{OX} \left( W_n L_n + W_p L_p \right) = C_{OX} L_{MIN} \left( W_n + W_p \right) = C_{OX} L_{MIN} \left( 7 W_{MIN} \right)$$

But C<sub>REF</sub>=4C<sub>OX</sub>W<sub>MIN</sub>L<sub>MIN</sub> so  $C_{IN} = \frac{7}{4} C_{REF}$

Since there are 8 inputs at the first level of logic, the gate area at the first level of logic is

$$A_{GATE1} = 8 \bullet (L_{MIN} \bullet 4W_{MIN} + L_{MIN} \bullet 3W_{MIN}) = 56L_{MIN}W_{MIN}$$

At the second level of logic, the 2-input NOR gate will have  $W_n = W_{MIN}$  and  $W_P = 6W_{MIN}$  so the gate area at the second level of logic is

$$A_{GATE2} = 2 \bullet (L_{MIN} \bullet W_{MIN} + L_{MIN} \bullet 6W_{MIN}) = 14L_{MIN}W_{MIN}$$

And at the third level of logic, the inverter will have a gate area of

$$A_{GATE3} = (L_{MIN} \bullet W_{MIN} + L_{MIN} \bullet 3W_{MIN}) = 4L_{MIN}W_{MIN}$$

So the total gate area is A  $_{\text{TOTAL}} = \sum_{i=1}^{} A_{_{GATEi}} = 74 L_{_{MIN}} W_{_{MIN}}$

For the inputs on the 2-input NAND gates,  $W_n = 2W_{min}$ ,  $W_p = 3W_{min}$  so the capacitance on each input is  $C_{IN} = C_{OX} (W_n L_n + W_p L_p) = C_{OX} L_{MIN} (W_n + W_p) = C_{OX} L_{MIN} (5W_{MIN})$ But  $C_{REF} = 4C_{OX}W_{MIN}L_{MIN}$  so  $C_{IN} = \frac{5}{4}C_{REF}$  Since there are 8 inputs at the first level of logic, the gate area at the first level of logic is

$$A_{GATE1} = 8 \bullet \left( L_{MIN} \bullet 2W_{MIN} + L_{MIN} \bullet 3W_{MIN} \right) = 40L_{MIN}W_{MIN}$$

At the second level of logic, the 4-input NOR gate will have  $W_n = W_{MIN}$  and  $W_P = 12W_{MIN}$  so the gate area at the second level of logic is

$$A_{GATE2} = 4 \bullet \left( L_{MIN} \bullet W_{MIN} + L_{MIN} \bullet 12W_{MIN} \right) = 52L_{MIN}W_{MIN}$$

And at the third level of logic, the inverter will have a gate area of

$$A_{GATE3} = (L_{MIN} \bullet W_{MIN} + L_{MIN} \bullet 3W_{MIN}) = 4L_{MIN}W_{MIN}$$

So the total gate area is A <sub>TOTAL</sub> =  $\sum_{i=1}^{3} A_{GATEi} = 96L_{MIN}W_{MIN}$

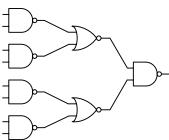

For the inputs on the 2-input NAND gates,  $W_n = 2W_{min}$ ,  $W_p = 3W_{min}$  so the capacitance on each input is  $C_{IN} = C_{OX} \left( W_n L_n + W_p L_p \right) = C_{OX} L_{MIN} \left( W_n + W_p \right) = C_{OX} L_{MIN} \left( 5W_{MIN} \right)$

But  $C_{\text{REF}}=4C_{\text{OX}}W_{\text{MIN}}L_{\text{MIN}}$  so  $C_{\text{IN}}=\frac{5}{4}C_{\text{REF}}$

Since there are 8 inputs at the first level of logic, the gate area at the first level of logic is

$A_{GATE1} = 8 \bullet \left( L_{MIN} \bullet 2W_{MIN} + L_{MIN} \bullet 3W_{MIN} \right) = 40L_{MIN}W_{MIN}$

At the second level of logic, the 2-input NOR gate will have  $W_n = W_{MIN}$  and  $W_P = 6W_{MIN}$  so the gate area at the second level of logic is

$$A_{\text{GATE2}} = 4 \bullet \left( L_{\text{MIN}} \bullet W_{\text{MIN}} + L_{\text{MIN}} \bullet 6 W_{\text{MIN}} \right) = 28 L_{\text{MIN}} W_{\text{MIN}}$$

And at the third level of logic, the NAND gate will have a gate area of

$$A_{GATE3} = 2 \bullet (L_{MIN} \bullet 2W_{MIN} + L_{MIN} \bullet 3W_{MIN}) = 10L_{MIN}W_{MIN}$$

So the total gate area is A  $_{\text{TOTAL}} = \sum_{i=1}^{3} ~A_{_{GATEi}} = 78 L_{_{MIN}} W_{_{MIN}}$

Problem 5 For a k-input NOR gate with k=3, if OD=1 and equal to that of the reference inverter  $L_n=L_p=L_{min}$ ,  $W_n=W_{min}$  and  $W_p=3kW_{min}=9W_{min}$

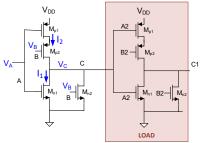

Problem 6 Circuit is shown below but trip point determined by the input gate only, not affected by the Load.

There are two scenarios that cause the output to transition. One is when one of the inputs transitions and the other input is low. The other is when both inputs transition together. We will denote these as Case 1 and Case 2.

a) Case 1. Assume B input is 0 and A input transitions between 0 and 1. If the B input is 0, Mn2 is in cutoff. Trip point will occur when VA=VC and this will happen when Mn1 and MP1 are in Sat region. Since Mn1 and Mp1 are in saturation,

$$I_{1} = \frac{\mu_{n}C_{OX}W_{n1}}{2L_{n1}}(V_{A}-V_{THn})^{2}$$

$$I_{2} = \frac{\mu_{p}C_{OX}W_{p1}}{2L_{p1}}(V_{A}-V_{DD}-V_{THp})^{2}$$

Equating these two currents and solving for VA, obtain

$$V_{A} = V_{TRIP} = \frac{\left(V_{THn}\right) + \left(V_{DD} + V_{THp}\right) \sqrt{\frac{\mu_{p}}{\mu_{n}} \frac{W_{p1}}{W_{n1}} \frac{L_{n1}}{L_{p1}}}{1 + \sqrt{\frac{\mu_{p}}{\mu_{n}} \frac{W_{p1}}{W_{n1}} \frac{L_{1n}}{L_{p2}}}$$

Case 2 Assume A and B inputs are connected together. In this scenario, Mn1 and Mn2 are connected in parallel and serve as a single device with effective width equal to 2Wn1. Again, trip point will occur when VA=VC and this will happen when the parallel combination of MN1 and MN2 is in saturation and when MP1 is in saturation. We thus have

$$I_{1} = \frac{\mu_{n}C_{OX}2W_{n1}}{2L_{n1}}(V_{A}-V_{THn})^{2}$$

$$I_{2} = \frac{\mu_{p}C_{OX}W_{p1}}{2L_{p1}}(V_{A}-V_{DD}-V_{THp})^{2}$$

Equating these two currents and solving for VA, obtain

$$V_{_{A}} = V_{_{TRIP}} = \frac{\left(V_{_{THn}}\right) + \left(V_{_{DD}} + V_{_{THp}}\right) \sqrt{\frac{\mu_{_{p}}}{\mu_{_{n}}} \frac{W_{_{p1}}}{2W_{_{n1}}} \frac{L_{_{n1}}}{L_{_{p1}}}}{1 + \sqrt{\frac{\mu_{_{p}}}{\mu_{_{n}}} \frac{W_{_{p1}}}{2W_{_{n1}}} \frac{L_{_{1n}}}{L_{_{p2}}}}}$$

b) Since the first NOR gate is driving an identical device, the load on the first stage has a Fan-in of

$$\mathbf{FI}_{LOAD} = \left(\frac{\mathbf{3k+1}}{\mathbf{4}}\right)_{k=2} = \frac{7}{4}.$$

For a two-input NOR gate, there is only a single LH output

transition (there are two HL output transitions) and since the gates are sized for equal worst $t_{\text{REE}} = 7$

case rise-fall times,  $t_{LH} = \frac{t_{REF}}{2} \bullet FI_{LOAD} = \frac{7}{8} t_{REF}$

Problem 7

Since sized for equal worst-case rise-fall times with OD=1, we have  $\mathbf{t}_{PROP} = \mathbf{t}_{REF} \cdot \sum_{k=1}^{3} \mathbf{F}_{I(k+1)}$

It follows that

$$F_{I2} = \frac{3+k}{4}\Big|_{k=3} = \frac{3}{2}$$

$F_{I3} = \frac{3k+1}{4}\Big|_{k=2} = \frac{7}{4}$   $F_{I4} = \frac{20fF}{C_{REF}}\Big|_{CREF=4fF} = 5$

Thus  $t_{PROP}$ =8.25 $t_{REF}$ .

Problem 8. There are multiple solutions. One follows.  $\overline{F} = (\overline{AB} \cdot \overline{C}) + \overline{D}$

Gate Implementation